ComLAB/Requerimientos de sincronización

◀ sección anterior | sección siguiente ▶

Es importante resaltar que para el correcto funcionamiento del sistema de transmisión debemos garantizar una sincronización de la señal a nivel de símbolo (bit) y a nivel de palabras de código (byte). Para su logro en sistemas reales se cuenta, en general, con procedimientos síncronos y asíncronos. En el primer caso se garantiza una misma temporización en los equipos de un lado y otro de la cadena de transmisión, que es la situación que recreamos actualmente en comLAB para la sincronización de bit (empleando una temporización única para todos los módulos). En las soluciones asíncronas, bien puede introducirse una señalización que permita identificar instantes de sincronización (por ejemplo, a nivel de tramas de bits, o tramas de multiplexación), o bien mecanismos que permitan establecer una sincronización automática mediante subsistemas adaptativos que maximizan la calidad de la recepción a nivel de símbolo, palabra de código (byte), trama multiplexada, etc.

Sincronismo de palabra de código (byte)

En la configuración actual del comLAB, que carece de tales medios de sincronización a nivel de palabra de código (byte), recurriremos a ajustar el retardo que introduce el canal ideal para garantizar que se produzca sincronismo a este nivel. Para ello se debe tener en cuenta que el codificador de línea introduce –por sí mismo– un retardo que, tras la recepción digital, equivale a Ns bits (donde Ns coincide con la extensión de los pulsos básicos empleados en la modulación/codificación de línea en número de periodos de símbolo, ver el artículo Filtrado en coseno alzado en glossaLAB). Si las palabras de código (byte) son de b dígitos binarios y el proceso de modulación/demodulación introduce un retraso de Ns⋅k bits (donde k es el número de bits que codificamos por cada símbolo transmitido, que normalmente será log2M bits, donde M es el orden de la modulación), será necesario agregar un retraso r en la transmisión de la señal (adelantarla no sería causal), de modo que al combinar ambos el retraso total sea equivalente a b y de ese modo pueda reconstruirse las palabras de código (bytes) y, en consecuencia, las muestras de la señal. Es decir, si Ns⋅k < b, entonces r = b - Ns⋅k [dígitos binarios] que en la señal continua de línea (muestreada a razón de Ms muestras por periodo de símbolo o dígito binario) se traduce en un retraso de r = (b - Ns⋅k) Ms [muestras].

En lo que concierne a este retardo, obsérvese que si Ns⋅k = b, la palabra de código quedará bien ordenada sin necesidad de añadir ningún retardo adicional, pero si es mayor, la diferencia con un múltiplo de b deberá de compensarse del mismo modo. Es decir, llamando E al resto de la división de Ns⋅k por b, es decir E = mod(Ns⋅k, b), el retardo de la línea que habría que introducir sería de r = (b - R)⋅Ms [muestras].

Obsérvese, que si el canal fuera multicanal (p.ej. estéreo) el número de bits a sincronizar no será el de una sola muestra, sino la de las muestras de los c canales multiplexados, lo que podemos determinar cambiando b en las relaciones anteriores por b' = c⋅ b.

Sincronismo para la comparación de señales en el dominio del tiempo

Otro requerimiento de sincronización, al que nos hemos referido en el apartado Comparación de señales en puntos diferentes de la cadena de transmisión de la sección Visualización y medida de las señales, ocurre en el ámbito de la visualización temporal y comparación de señales en dos puntos diferentes de la cadena de transmisión (P1 y P2), cuando los bloques que separan ambos puntos introducen un retardo, τ. Una comparación adecuada de las distorsiones ocurridas al atravesar los subsistemas intermedios mediante un osciloscopio o un medidor de error requiere un alineamiento de las señales de modo que la señal en P1 se retrase –antes de la entrada en el osciloscopio– lo mismo que la señal al pasar de P1 a P2, es decir, τ. El ajuste de esos tiempos puede hacerse teniendo en cuenta las operaciones realizadas en los bloques. Por ejemplo,

- Un filtro FIR de orden N como el empleado para evitar aliasing introduce un retardo de grupo (N-1)/2.

- El modulador/demodulador para códigos basado en pulsos en raíz cuadrada de coseno alzado introduce un retardo de Ns [bits] si la modulación es binaria (donde Ns es la duración en tiempos de símbolo de los pulsos en raíz cuadrada de coseno alzado), o Ns∙k [bits] (donde k es el número de bits que codificamos por cada símbolo transmitido).

- La combinación de las operaciones de cuantificación-modulación-demodulación-reconstrucción, teniendo en cuenta que la de modulación/demodulación es a nivel de bits y la de antes y después de la cuantificación/reconstrucción es a nivel de muestra, ya que los bits se reagrupan en el reconstructor, el retraso acumulado entre la entrada del cuantificador y a la salida de su reconstrucción será de R/b, donde R representa el retardo que teníamos a nivel de bit y b el número de bits que se agrupan por cada palabra de código para reconstruir el valor de las muestras.

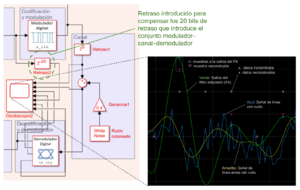

La Figura 10 ilustra la comparación realizada a la salida del receptor digital respecto a la entrada del modulador en virtud del retraso introducido. En este ejemplo la modulación es de orden M = 4, k = log24 = 2, Ns = 10, en consecuencia se introduce un retraso de 10∙2 = 20 bits. Como puede observarse la comparación produce un alineamiento perfecto entre la señal a la entrada del modulador y a la salida, lo que nos permite apreciar que en todos los casos visualizados se produce una coincidencia exacta del código a la entrada y salida del canal digital.

Sin embargo, si tuviéramos un retardo en el canal de r muestras de la señal, entonces el retraso acumulado en modulación-canal-demodulación será Ns∙k + r∙k / Ms bits. Y cuando se trata de comparar la señal en puntos previos a la cuantificación con los posteriores a la reconstrucción, teniendo en cuenta que cada muestra de la señal diezmada se codifica con b bits, el retraso acumulado en número de muestras de la señal diezmada será: (Ns∙k + r∙k / Ms ) / b muestras.

A modo de ejemplo, si contamos con una modulación de orden M = 4, Ns = 5, Ms = 20 y un retardo en el canal de 60 bits, deberíamos introducir un retraso de 16 bits en la señal de entrada del modulador para visualizarla en sincronía con la señal de salida del demodulador. Y si la cuantificación fuera de 8 bits, el retraso entre la señal antes de la cuantificación y después de la reconstrucción será de 16/8 = 2 muestras.

Determinación del retraso entre señales que se desea comparar

Entender los procesos involucrados en las diferentes etapas supone ser capaces de determinar el retraso que cabe esperarse entre las señales entre dos puntos del circuito y, como tal, su cálculo correcto es un signo de comprender lo que cada etapa hace. Por tanto, no debería evitarse realizar tal cálculo y en caso de error, debería revisarse con cautela cada una de las operaciones involucradas hasta acertar con el valor correcto. No obstante, obsérvese que si hiciéramos la correlación cruzada de las señales a comparar ésta alcanzaría un máximo en el tiempo de retraso relativo entre las señales. Esto es lo que hace el bloque nativo de Simulink Find Delay representado en la Fig. 11 para ofrecer una medida del retraso medido.

También podemos recurrir al propio osciloscopio (bloque nativo Scope) para consultar la sincronización entre dos señales dadas de forma cuantitativa o gráfica, respectivamente.